2014年10月8日 17:34

富士通研、ミリ波レーダの低コスト化が図れるCMOS送受信チップを試作

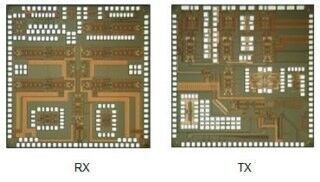

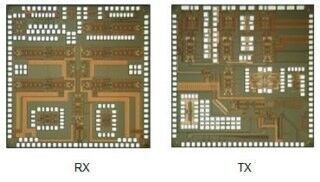

富士通研究所は10月8日、低コスト化が可能な半導体プロセスであるCMOSを使用したミリ波レーダ用送受信チップを試作し、近距離検知性能向上を実現することに成功したと発表した。

詳細は、10月5日よりイタリア・ローマで開催される国際会議「EuMC 2014(European Microwave Conference 2014)」にて発表される。

自動車などで用いられるミリ波レーダは、使用する電波が76~81GHzと高い周波数のミリ波を使用するため、従来はSiGeバイポーラトランジスタなどの特殊な半導体を用いる必要があった。しかし近年、低コスト化が可能なCMOSでも、ミリ波回路の実現が可能になってきた。CMOSは、従来のSiGeバイポーラトランジスタに比べて低い電源電圧で動作可能なため消費電力を小さくでき、ミリ波領域においておおむね同等の性能を示すものの、低周波領域でのノイズ成分が大きいという問題があった。ミリ波レーダの場合、発振器のミリ波信号を送信し、障害物で反射してきた信号と元の送信信号との差分を比較することで、障害物の距離・速度・方位の検出を行っている。この中で、近い距離にある反射の弱い歩行者などの検知性能を向上させるには、低周波領域のノイズを低減する必要がある。