Mentor、パワーアウェア高速設計向けにSI/PI解析ツールの最新版を発表

HyperLynx SI/PIの新機能には、パワーアウェアIBISモデルのサポート、DDR4/LPDDR4(ローパワー設計向け次世代メモリ)の妥当性確認ためのDDRxウィザードが含まれている。

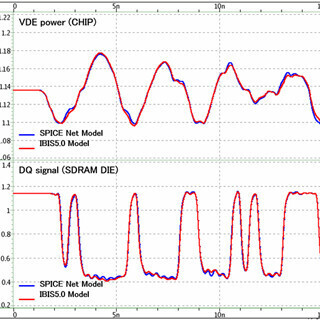

追加されたパワーアウェアSIシミュレーションは、DDR3やDDR4をはじめとする高速パラレルリンクの精密なモデル化と信号性能解析を実現。パワーアウェアIBIS v5.0モデリングに基づき、同時スイッチングノイズ(SSN)、タイミングの電源効果、SIを正確にシミュレートするほか、最新JEDEC規格に準拠するDDRxウィザードで、次世代DDR4とLPDDR4を含むあらゆる種類のDDRおよびLPDDRメモリを検証する。

他手法と比べて5倍から10倍高速な統合Sパラメータ抽出とシミュレーションを実現。高性能のDC電圧降下/熱コシミュレーションは、電圧降下、高電流エリア、結果として生じる温度変化を、競合ソリューションと比較して何桁も速く予測する。

最新バージョンは、非理想電源の効果を表すIC向けのIBIS(Input/output Buffer Information Specification)v5.0モデルをサポートしている。同機能は、プリドライバ効果や供給電圧降下によるスイッチング動作の遅れなど、供給される電流を正確にモデル化するとともに、バッファのキャパシタンスのモデル性能を高める。パワーアウェアIBISモデルは、DDRx解析を含むすべてのタイプのシミュレーションに適用可能で、タイミングの電源効果と信号品質を確認できる。HyperLynxは、次世代メモリのインターコネクトを設計する際に決定的に重要となるSSNをモデル化する。

DDRxウィザードは最新のJEDEC規格に準拠しており、DDR4とそのローパワー版に相当するLPDDR4など、すべての種類のDDRメモリを検証できる。また、DDR3ならびに次世代のDDR4メモリシステムを完全に検証するためにアイダイアグラムを生成する。シミュレーション内の個々のビットすべての妥当性を確認するために、DDRxとLPDDRxのための統合タイミング解析などアイダイアグラムに基づくメトリクスチェックを実行する。

適切なスタブ除去に伴うビアを正確にシミュレーションするためのバックドリルのサポート。

「what-if」シナリオを迅速に確立し、ドリルを有効化あるいは無効化する。

Touchstone Viewer機能は、IEEE 802.3 Ethernet仕様に定義されたILDやICRをはじめとするメトリクスに基づいて計算し、標準からミックスモードへのSパラメータモデル変換を含む、インターコネクトの差動クロストーク特性を評価する。

SerDes機能の追加によって、新しいIBIS 6.0の機能、FastEyeウィザード内のCTLEイコライゼーション、バッチAMI実行のための128b/130bエンコーディングとコンフィギュレーションファイルをサポートする。