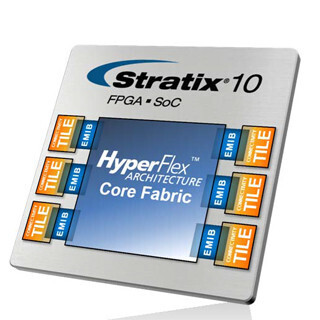

Altera、14nmプロセスFPGA「Stratix 10」のアーキテクチャの詳細を公開

Stratix 10シリーズは、ARM Cortex-A53を4コア搭載し、コア性能は従来比で2倍に向上させつつ、70%の消費電力低減を実現している。また、550万ロジックエレメント(LE)を搭載し、10TFLOPSを超す性能を提供するハイエンド製品として位置づけられている。

こうした低消費電力と高い性能を実現するのが「HyperFlex」となる。従来、ロジックは容量の増大により、配線遅延が性能向上の足かせとなってきた。バス幅の拡大で解決を図る考えもあるが、配線が過密化するという課題があった。

HyperFlexでは、すべての配線セグメントの中にレジスタ(Hyper-Register)を入れることで、配線のパスを短くでき、これにより従来比で2倍以上の配線速度を実現した。あるアーリーアダプタ(データセンター業者)の場合、Stratix Vで250MHzのパフォーマンスで、サーチの機能やデータ演算などのオフロードを実現していたが、それをStratix 10に置き換えたところ、5個のStratix Vを1個のStratix 10に移行できることが判明したほか、ワイヤレス光スイッチの場合では、ロジックエレメント(LE)数は900Kから650Kに減ったものの、動作周波数は350MHzから700MHzに向上し、2倍のコア性能、バス幅の縮小による30%の実装面積削減、40%の消費電力削減を実現したとしている。

また、LE数の削減としては、Intelのシリコンインタポーザを用いずに低コストで2.5Dパッケージを実現するソリューション「Embedded Multi-die Interconnect Bridge (EMIB)」を採用し、ホモジニアス(単一)なFPGAのモノリシックダイと、さまざまな機能を有する「タイル」と呼ぶ自社設計のダイをEMIBで接続することで実現している。このタイルは主にトランシーバで、最初のタイルとしてはPCI Exoress(PCIe) Gen3が搭載されるとするが、ほかのプロトコルも搭載可能としており、PCIe Gen4なども将来的に対応していく計画であるとしており、これにより次世代通信規格の容易なサポートと、低消費電力化の両立を図ることが可能であるとしている。さらに、新たなセキュリティ機能として「Secure Device Manager(SDM)」を搭載したとする。これはセクタ単位の認証と暗号を提供するもので、FPGAのデバイス自体を独立して認識させることができるSARMベースの「PUF(Physically Undonable Function:プロセスのバリエーションから生成された乱数)」を設定することで、FPGA内のルート鍵を暗号化、オフライン攻撃によるルート鍵の特定を防止することを可能としたほか、FPGA内部でセキュアなセクタと非セキュアなセクタを構築して、それぞれを個別に認識、実行を可能とした。加えて、個別のエンティティによる多様素認証鍵の作成も可能だという。

なおStratix 10は、同社の設計開発ツールである「Qurtus II」ならびにサブスクリプションとして提供される「Spectra-Qエンジン」の「Hyper-Awareデザインフロー」はHyperFlexに最適化されており、これを活用することでを設計期間の短縮が可能となるほか、同社が提供するPowerSoc「Enpirion EM1130」を搭載したEnpirion電源モジュールもStratix 10に最適化されたものが提供されるとのことで、これにより、Intelの提供するSmartVoltage ID(SmartVID)の省電力機能を活用することが可能となるとしている。