ISC 2015に見る今後のスーパーコンピューティングの方向性 (6) IntelのAlan Gala氏が語った将来のシステムの方向性(後編)

前回最後に示した再構成されたシステムは、CPUを肥大化させず、かつ、消費電力の小さなオンパッケージのメモリだけを使っており、大幅に消費電力が低くなっているが、まだまだ、改善が必要である。

演算に必要なエネルギーに比べてデータ伝送のエネルギーの方が大きいという時代になっているので、データ伝送のエネルギーの低減について考える。データ伝送路の寄生容量がCでそれを電源電圧Vで充放電すれば、CV2のエネルギーを消費するので、回路的にCやVを減らさないとデータ伝送に必要なエネルギーは減らせないと思うかも知れないが、そんなことはない。

図3.8のように4ビットの入力データを8本の信号線を使うように符号化して送り、それを受け側で4ビットに戻すというやり方をすると伝送に必要なエネルギーを減らすことができる。例えば、2ビットのデータ値の0~3に応じて4本の信号線の中の1本を選択して信号を送れば、1本の信号線を駆動するエネルギーで2ビットのデータを送れる。ただし、信号線の本数は多く(この例では2倍)必要になる。

1ビットの信号を送るのに必要な線は2本であるが、これを1.5倍の3本、2倍の4本のように本数を増やしていった時に必要な伝送エネルギーを示したものが図3.9である。6本の線は、物理的な線を論理的に何本の線として使うかという符号化のやり方の違いである。

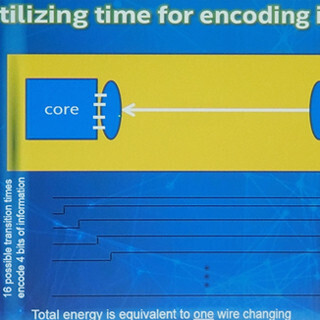

逆にすべての信号を1本の線を使って送ることで伝送エネルギーを減らすこともできる。図3.10に示すように、4ビットの信号を0~15とみなし、この値で、信号をスイッチするタイミングを変える。受け側では、どのタイミングで信号がスイッチしたかが分かれば4ビットの信号を受け取ることができる。ただし、4ビットを単純にシリアルに送れば4クロックで済むが、このように符号化すると16クロック必要となり、4倍の伝送時間が掛かる。

つまり、処理速度は遅くなるが、1ビットを送るのに必要なエネルギーを減らすことができるわけである。

図3.11は、信号線の本数を1/2、1/4、1/8と減らしていった場合の、消費エネルギーと伝送速度のグラフである。一番上のグラフが伝送に必要な総エネルギー、次のグラフが伝送に必要なダイナミックエネルギー、一番下のグラフが伝送速度を示し、右上がりのグラフがリークによる消費エネルギーを示している。○アーキテクチャ的に未開拓分野を開拓する

図3.12の右下の棒グラフはSpecIntとSpecFPのプログラムの実行状況を示すもので、各棒グラフの下側の青い部分は有効な処理を行っている時間の比率で、赤の部分はコアが予測外れで止まっている時間、緑の部分はメモリが予測外れで止まっている時間の比率を示している。

これを見ると、予測外れのために、プロセサは半分程度の時間しか有効な仕事をしていないことが分かる。

HPCの処理は、長い時間スケールでは、基本的に同じ処理の繰り返しになる。しかし、ハードウェアの予測機構は短い繰り返しはうまく処理できるが、長いサイクルの繰り返しにはうまく対応できない。これを、コンパイラやプログラミングモデルで繰り返しを明示して処理できるようにして、予測外れを低減する。そして、そのような繰り返しの処理を効率よく実行できるようにハードウェアを最適化すれば、性能もエネルギー効率もあがる。

○結論

メモリテクノロジは10倍から100倍の改善の余地がある。ただし、その改善をフルに利用するためには、メモリシステムの造りを考え直す必要がある。

電力は問題であるが、システム規模の2~4倍の増加は可能。

その他の改善を集めると、さらに2~4倍の改善ができる。最後に述べた予測性の改善は、シングルスレッドの実行性能を改善できる。

これらを総合すると、10ExaFlopsへの道は見えてきており、100ExaFlopsもなんとかなりそうという前向きの結論であった。