Hot Chips 27 - 中国Phytiumの64コアARMv8サーバプロセサ「Mars」(中編)

○Xiaomiコアのフロントエンド

Xiaomiコアのフロントエンドは、32KBのL1命令キャッシュを持ち、分岐予測は2048エントリのBTB(Branch Target Buffer)とTAGE(TAgged GEometric history length)分岐予測を用いている。また、512エントリの間接分岐予測器と、48エントリのリターンスタックを持っている。

そして、Loop Detectというブロックを持ち、ループの全命令が命令バッファに収まっている場合は命令キャッシュ側から命令を読まなくて済むようになっている。この機構は、少し前のIntelのCoreプロセサでも採用されていたことがある。

多種の分岐予測機構を持ち、Loop Detectを行うなど、Xiaomiコアは、かなり高級なメカニズムを実装している。

○XiaomiコアのOut-of-Order実行機構

Xiaomiコアは1サイクル最大4命令をデコードすることができ、また、最大4命令をリネームしてディスパッチすることができる。リオーダバッファは160命令を保持、物理レジスタは192個とXeonなどのハイエンドコアに劣らない量のOut-of-Order実行資源を積んでいる。

Xiaomiコアは4つの整数演算ユニットを持ち、その内の1つはマルチサイクルの整数演算や分岐命令の処理が行える。

浮動小数点演算は64bitの演算器を2個持ち、128bitのSIMD演算を行う場合は2個の演算器を繋いで処理するようになっている。

ロード/ストアユニットは24エントリのキューを持ち、32KBのL1データキャッシュをアクセスする。ロードからそのデータを使えるようになるまで4サイクルというのはちょっと遅い感じであるが、致命的ではない。

○キャッシュコヒーレンシ機構

Marsシステムでは、Hawkと呼ぶキャッシュコヒーレンシプロトコルで全キャッシュのコヒーレンシが維持されている。Hawkはパケットを使うディレクトリベースのMOESIライクのコヒーレンシプロトコルであるという。

○パネル間を接続するメッシュネットワーク

Marsチップ内のパネル間の接続はルーティングセルを使った4×2のメッシュ接続になっている。この接続に限ればルーティングセルは3ポートで良いが、実際には次の図のようにルーティングセルは6ポートのスイッチになっている。残りの3ポートはIOUやMIU、あるいはカスケードと書かれており、I/Oやメモリへの接続や他のチップとの接続に使われると思われる。

ホップあたりの遅延は3サイクルでルーティングセルあたりのバンド幅は384GBとなっている。但し、これは6ポートのIn/Outの合計と考えると、1リンクでは32GB×2ということになる。

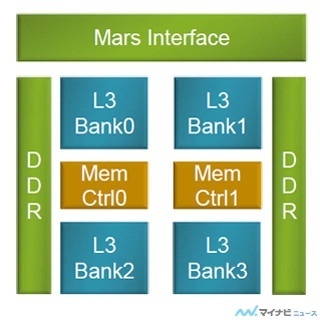

○Cache and Memoryチップ

CMCチップは16MBのL3キャッシュと2チャネルのDDR3 DIMMチャネルを集積している。従って8個のCMCチップの合計では128MBのキャッシュを持つことになる。次の図ではDDR3-800となっているが、これはDDR3-1600の間違いで、CMCあたりのメモリバンド幅は25.6GB/sとなる。CMCとCPUチップの接続は高速シリアル伝送ではなく、独自の並列伝送のインタフェースを使っている。シリアル-パラレル変換の時間ロスが無く高速というのが理由であるが、信号だけでも1024本であり、グランドの接続を含めると1500~2000ピンが必要となる。この接続が、Marsチップ全体で3000ピンを必要とする主因になっていると考えられる。

○メモリアクセスのバンド幅とレーテンシ

ローカルのL1キャッシュをヒットした場合は2サイクル、ローカルのL2キャッシュヒットは8サイクル、同一パネルの他方のL2キャッシュのヒットは20サイクル。直結されているCMCのL3キャッシュヒットは36サイクルでメッシュを経由しないでCMCを通してDDR DIMMをアクセルする場合は70サイクル程度のアクセスタイムとなる。

メモリの実効読み出しバンド幅は12.8GB/s、実効書き込みバンド幅は6.4GB/sと書かれており、DDR3-1600のピークバンド幅である25.6GB/sと比べると、実効バンド幅は、読み出しは1/2、書き込みは1/4となっている。

これはパネルとネットワークは2GHzで動作し、CMCは1.5GHz動作とした場合の値である。

(後編はコチラ)