2015年8月10日 13:00

ISC 2015に見る今後のスーパーコンピューティングの方向性 (10) 将来のノードアーキテクチャはどうなるのか(4)

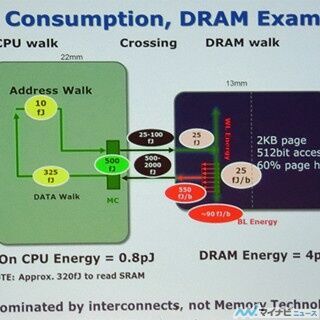

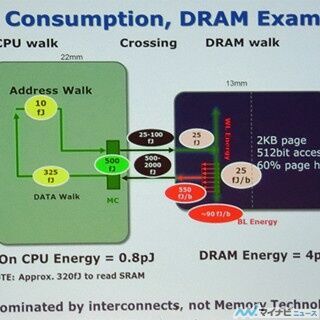

○信号を伝送するために必要なエネルギーが問題

図4.16は、計算処理のための回路の消費エネルギーとブロック間を接続するグローバルな配線を駆動するための消費エネルギーが、微細化でどのように変化したかを示すものである。回路の消費エネルギーは45nmプロセスから7nmまでに1/6に減少しているが、配線の駆動エネルギーは、60%にしか減少しない。結果として、微細化に伴ってグローバル配線を駆動するエネルギーの比率が大きくなる。このため、グローバル配線のエネルギーを減らすことが重要となる。

図4.17は計算処理を行うループを大まかに描いたものである。右側の演算部分では、演算の実行のためにレジスタから8バイトのオペランドを2個読み出し、8バイトの結果を1個書き戻す。この図ではDRAMからチップ上の2次(あるいは3次)キャッシュに読み込まれるのは1ビットとなっているが、これは1回に64バイトをDRAMから読み込むとしても、キャッシュミスによるメモリの読み込みは平均的には512演算に1回程度と見ているからである。

この図は2012年頃の22nmプロセスを想定しているが、右の演算部にデータを用意し、演算結果を格納するというデータの移動に掛かるエネルギーが82pJで、右側の実際に演算命令を実行する部分は14pJしかエネルギーを使っていない。