2015年2月24日 12:18

富士通研、CPU間の大容量伝送に向けて多並列化が可能な光送受信回路を開発

富士通研究所は2月23日、今後のサーバやスパコンのCPU間大容量データ伝送の実現に向けて、多並列化が可能な光送受信回路を開発したと発表した。

詳細は、2月22日から米国サンフランシスコで開催されている「国際固体素子回路会議ISSCC 2015(IEEE International Solid-State Circuits Conference 2015)」にて発表される。

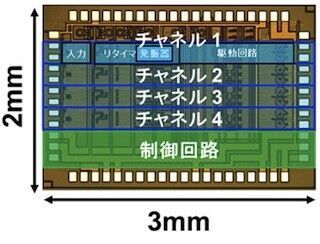

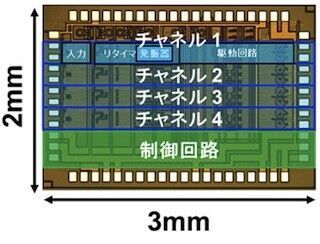

データの大容量化に向けては、高速化と高密度化の両立が必要だが、高速化によってCPUと光インターコネクト間の接続でノイズによる波形劣化が顕著になる。高速動作を阻害するノイズとして、時間方向に波形がぶれる現象が発生するため、信号を処理する際のタイミングが合わなくなる。この修復には、時間方向の波形劣化を修正する回路も含めた回路全体の高密度化技術が要求される。現状では、光素子の駆動回路は複数チャネルを1つのICに集積化できているが、時間方向の波形の修復を行うリタイマ回路には、高速な発振回路があり、コイルを内蔵することから互いに干渉するため0.5mm以上の配置間隔が必要だった。このため、複数のチャネルの回路を集積化した場合、これが小型化を妨げる大きな要因となっていた。