高速なDDRメモリ搭載システムの設計/開発を強力にサポート - 不良解析作業の効率化を実現するDDRデバック・ツールキット

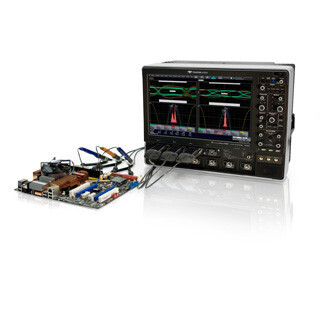

テレダイン・レクロイは、DDRメモリのコンプライアンス試験ソリューションに加えて、DDRデバック・ツールキット(DDR Debug Toolkits)を提供し、豊富なデバッグ機能によりDDRを用いたシステムの設計/開発を強力にサポートします。

パソコンのメインメモリとして知られるDDRメモリですが、DDR、DDR2、DDR3と進化し、現在最新の規格はDDR4となっています。また、パソコンだけでなく組み込み系の機器にも広く採用されています。DDRに関する規格はJEDEC(半導体技術協会)が制定していて、各計測器メーカーからこの規格に準拠したコンプライアンス試験ソリューションが提供されています。しかしながら、JEDECの規格は半導体そのものの仕様を規定しているだけで、途中の伝送線などについては考慮されていません。従って、基板の実装状態などにより通信エラーが起きる可能性が指摘されています。特に、データレートが高速化するにつれてこうした影響が大きくなります。従来のコンプライアンス試験ソリューションでは、適合/不適合の判定が行われるのみで、デバッグにつながる不良解析情報は得られませんでした。

DDRデバック・ツールキットは、こうした現場の声に応えるために、評価、不良解析を目的としたパッケージとなっています。

○強力なアイパターン解析

アイパターンは高速シリアル・インタフェースの信号品質試験で用いられる最も一般的で強力なツールですがJEDECでは、DDR4になるまで仕様に記載されていませんでした。しかしながら、アイパターンは、DDR信号評価の事実上の標準ツールとなっていました。DDRデバッグ・ツールキットではアイパターンが描けるだけでなく、DDR2やDDR3の信号に対してもDDR4同様の考え方でマスクを作成し表示することで、信号マージンの確認ができます。ただし、メモリの信号は書き込み(Write)も読み取り(Read) も同一バス上を流れますが、それぞれ経由してくる線路長が異なるため信号品質が異なるので別々に分離して評価しなければなりません。データ信号DQのWrite信号とRead信号は、ストローブ信号DQSに対して位相が90度異なっています。図2では、DQ信号とDQS信号のペアを5組、10個のアイパターンを同時に表示解析している様子を示しています。左上はReadのDQ(緑)とDQS(オレンジ)、真ん中上にはWriteのDQ(緑)とDQS(オレンジ)、右上はReadのDQS(緑)とClock(オレンジ)、左下はWriteのDQS(緑)とClock(オレンジ)、真ん中下には別の条件のReadのDQ(緑)とDQS(オレンジ)のアイが描かれています。

このように条件や信号の種類、タイミングを変えた多様なアイパターンを同時に描くことでシステムの動きを把握することが容易になります。

○DDRのジッタ解析

高速伝送の信号品質評価のもうひとつの鍵となるのがジッタの評価ですが、DDRにおいてはやはりDDR4で高速シリアル伝送で一般的なジッタ成分分離評価が導入され、より詳細なジッタの評価が求められています。注意しなければならないのは、DDRにおいては、Clock信号は連続していますが、DQやDQS信号はバースト状の信号で、上記のようにReadとWriteが混在しているので、必要な部分で選択的にジッタの計測を行わなければならないので工夫が必要です。

DDRデバッグツールでは、こうしたDDR特有のジッタ計測に対応し、かつ上記のアイパターン解析で説明したように最大5種類の条件でジッタの解析を行うことができます。図3は、2種類のジッタの様子を示していますが、左側は隣接レーンにデータが流れてクロストークが発生している状態、右側は隣接レーンのデータを止めてクロストークの発生を抑えた状態をしめしています。クロストークによってRj、Dj共に増加しています。

○DDR専用パラメータ解析

DDRデバッグ・ツールキットでは、もちろんJEDEC規格に準拠したパラメータ計測が行えます。パラメータは任意のものを選択でき、同時に12個まで同時に表示することができます。

DDRデバッグ・ツールキットでは、非常に多くのデータを基に統計情報が表示されるので、規格に対するマージンが確認できます。もちろんReadとWriteをそれぞれ別個に計測することができます。図3では、ジッタのパラメータの下にDDR専用のパラメータが表示され、クロストークの有無でこれらのパラメータがどう変化するかを確認することができます。

○解析ビットの選択

DDRのDQ、DQS信号がバースト状の信号なのでバーストの始まりにはプリアンブルがあり、それ以降の信号と振る舞いが異なります。DDRデバッグツールにおいては、アイパターンの描画を行う対象のビットを特定することができます。図4の左にはReadの第一ビットのみでアイパターンを描いているので、プリアンブルの動きが見てとれます。右側にはWriteのやはり第一ビットのみでアイパターンを描いています。逆に、第二ビット以降のビットだけでアイパターンを描くこともできます。

○まとめ

これまで見てきたように、DDRデバッグ・ツールキットでは、アイパターン、ジッタ、DDRパラメータを使った解析をReadとWriteを分離して解析することができるだけでなく、様々に条件を変えた結果を同時に表示、比較検証することができるので、不良解析作業を大幅に効率化することができます。

著者プロフィール

辻嘉樹

テレダイン・レクロイ・ジャパン

技術部

1990年の会社設立時から、オシロスコープを用いたアプリケーションに関する記事の執筆、セミナーの講師を続けている。

○パワエレ効率化を支援するモータ・ドライブ解析テクニカル・セミナー

テレダイン・レクロイ・ジャパンでは、モータ・ドライブ解析用オシロスコープ「MDA800シリーズ」の機能などを紹介するセミナーを3月6日に以下の概要にて開催します。

日時:2015年 3月 6日(金) 14:00~16:00(受付開始 13:30~)

会場:パレスサイドビル 東コア2F マイナビルーム X(東京都千代田区一ツ橋1-1-1)

定員:28名

参加費:無料(事前登録制)

主催:テレダイン・レクロイ・ジャパン

申込み:テレダイン・レクロイ・ジャパンWebサイトより